![Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working. Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.](https://i.imgur.com/JJi2Txh.png)

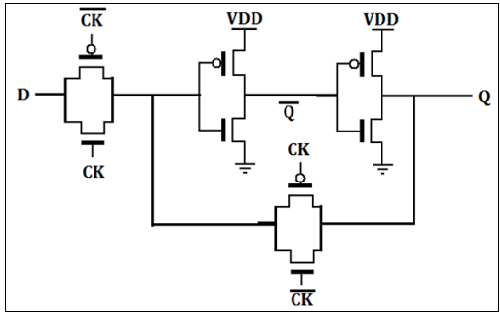

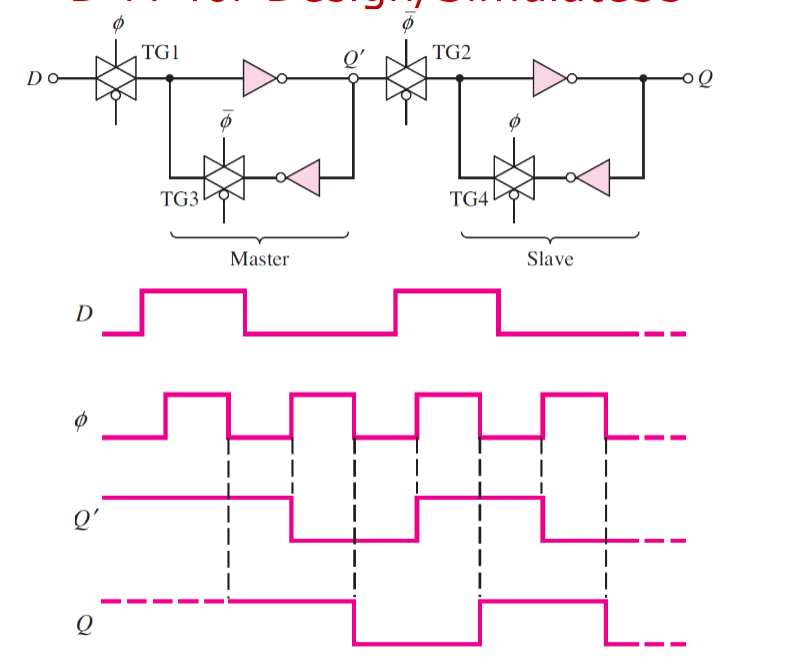

Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.

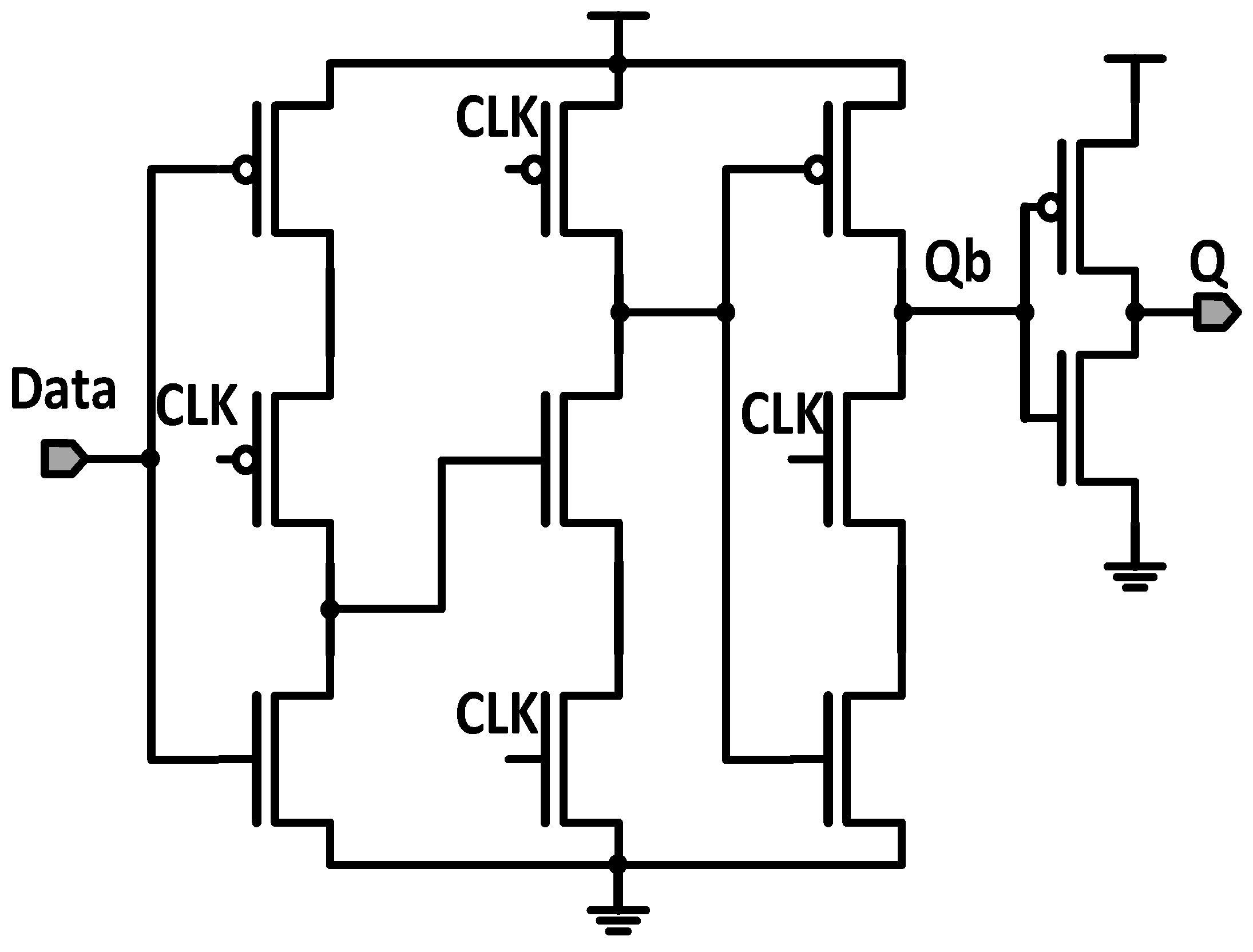

Electronics | Free Full-Text | Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips

![Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working. Implement D flip-flop using Static CMOS. What are other design methods for it? [10] OR Draw D flipflop using CMOS and explain the working.](https://i.imgur.com/ksiy7VH.png)

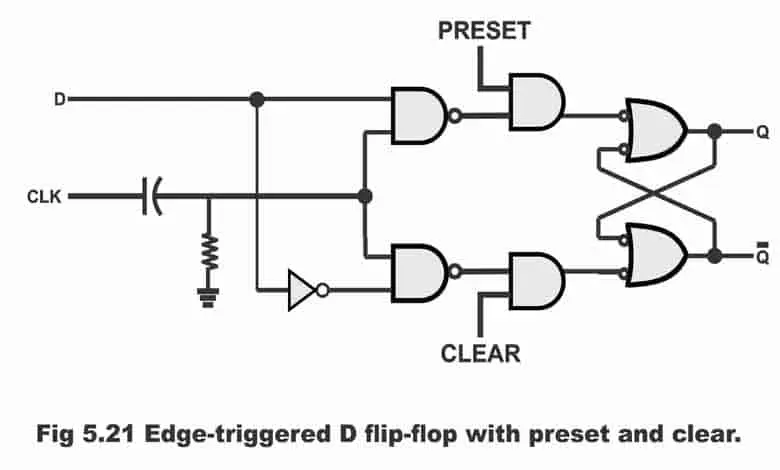

![PDF] Design of Positive Edge Triggered D Flip-FlopUsing 32nm CMOS Technology | Semantic Scholar PDF] Design of Positive Edge Triggered D Flip-FlopUsing 32nm CMOS Technology | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/0444588e0ac6ea62e3f4a32c6dd343f6d6705a1c/5-Figure5.1-2.png)